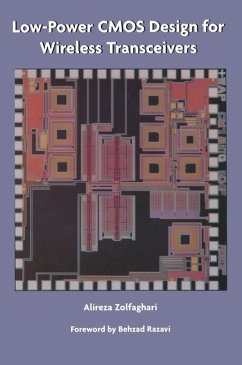

Low-Power CMOS Design for Wireless Transceivers provides a comprehensive treatment of the challenges in low-power RF CMOS design. The author addresses trade-offs and techniques that improve the performance from the component level to the architectural level.

Low-Power CMOS Design for Wireless Transceivers deals with the design and implementation of low- power wireless transceivers in a standard digital CMOS process. This includes architecture, circuits and monolithic passive components. The book is written for engineers and graduate students interested in learning about wireless networks, transceiver architectures, stacked inductors, design of RF front ends, and the design of a 2.4-GHz transceiver.

Low-Power CMOS Design for Wireless Transceivers deals with the design and implementation of low- power wireless transceivers in a standard digital CMOS process. This includes architecture, circuits and monolithic passive components. The book is written for engineers and graduate students interested in learning about wireless networks, transceiver architectures, stacked inductors, design of RF front ends, and the design of a 2.4-GHz transceiver.