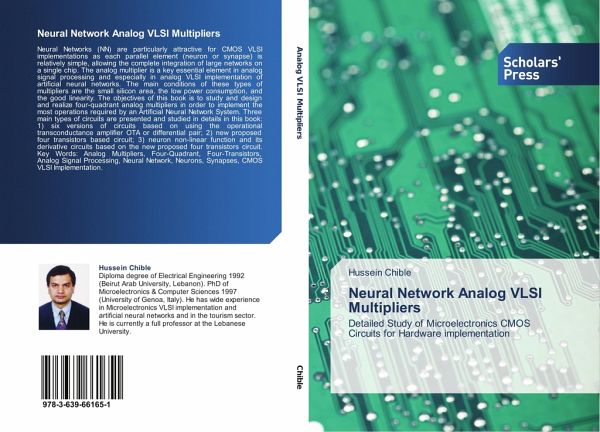

Neural Network Analog VLSI Multipliers

Detailed Study of Microelectronics CMOS Circuits for Hardware implementation

Versandkostenfrei!

Versandfertig in 6-10 Tagen

36,99 €

inkl. MwSt.

PAYBACK Punkte

18 °P sammeln!

Neural Networks (NN) are particularly attractive for CMOS VLSI implementations as each parallel element (neuron or synapse) is relatively simple, allowing the complete integration of large networks on a single chip. The analog multiplier is a key essential element in analog signal processing and especially in analog VLSI implementation of artificial neural networks. The main conditions of these types of multipliers are the small silicon area, the low power consumption, and the good linearity. The objectives of this book is to study and design and realize four-quadrant analog multipliers in ord...

Neural Networks (NN) are particularly attractive for CMOS VLSI implementations as each parallel element (neuron or synapse) is relatively simple, allowing the complete integration of large networks on a single chip. The analog multiplier is a key essential element in analog signal processing and especially in analog VLSI implementation of artificial neural networks. The main conditions of these types of multipliers are the small silicon area, the low power consumption, and the good linearity. The objectives of this book is to study and design and realize four-quadrant analog multipliers in order to implement the most operations required by an Artificial Neural Network System. Three main types of circuits are presented and studied in details in this book: 1) six versions of circuits based on using the operational transconductance amplifier OTA or differential pair; 2) new proposed four transistors based circuit; 3) neuron non-linear function and its derivative circuits based on the new proposed four transistors circuit. Key Words: Analog Multipliers, Four-Quadrant, Four-Transistors, Analog Signal Processing, Neural Network, Neurons, Synapses, CMOS VLSI Implementation.