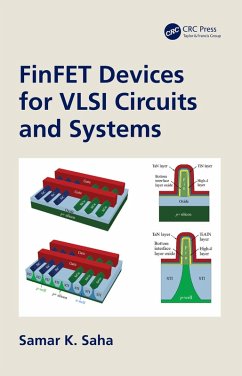

Samar K. Saha

FinFET Devices for VLSI Circuits and Systems (eBook, ePUB)

50,95 €

50,95 €

inkl. MwSt.

Sofort per Download lieferbar

25 °P sammeln

50,95 €

Als Download kaufen

50,95 €

inkl. MwSt.

Sofort per Download lieferbar

25 °P sammeln

Jetzt verschenken

Alle Infos zum eBook verschenken

50,95 €

inkl. MwSt.

Sofort per Download lieferbar

Alle Infos zum eBook verschenken

25 °P sammeln

Samar K. Saha

FinFET Devices for VLSI Circuits and Systems (eBook, ePUB)

- Format: ePub

- Merkliste

- Auf die Merkliste

- Bewerten Bewerten

- Teilen

- Produkt teilen

- Produkterinnerung

- Produkterinnerung

Bitte loggen Sie sich zunächst in Ihr Kundenkonto ein oder registrieren Sie sich bei

bücher.de, um das eBook-Abo tolino select nutzen zu können.

Hier können Sie sich einloggen

Hier können Sie sich einloggen

Sie sind bereits eingeloggt. Klicken Sie auf 2. tolino select Abo, um fortzufahren.

Bitte loggen Sie sich zunächst in Ihr Kundenkonto ein oder registrieren Sie sich bei bücher.de, um das eBook-Abo tolino select nutzen zu können.

The book provides the basic theory and operating principles of FinFET devices and technology. Accordingly, the book systematically presents an overview of FinFET device architecture and manufacturing processes, detailed formulation of FinFET electrostatic and dynamic device characteristics for IC design and manufacturing.

- Geräte: eReader

- mit Kopierschutz

- eBook Hilfe

Andere Kunden interessierten sich auch für

![Opto-VLSI Devices and Circuits for Biomedical and Healthcare Applications (eBook, ePUB) Opto-VLSI Devices and Circuits for Biomedical and Healthcare Applications (eBook, ePUB)]() Opto-VLSI Devices and Circuits for Biomedical and Healthcare Applications (eBook, ePUB)51,95 €

Opto-VLSI Devices and Circuits for Biomedical and Healthcare Applications (eBook, ePUB)51,95 €![Low Power Designs in Nanodevices and Circuits for Emerging Applications (eBook, ePUB) Low Power Designs in Nanodevices and Circuits for Emerging Applications (eBook, ePUB)]() Low Power Designs in Nanodevices and Circuits for Emerging Applications (eBook, ePUB)59,95 €

Low Power Designs in Nanodevices and Circuits for Emerging Applications (eBook, ePUB)59,95 €![Green Communication with Field-programmable Gate Array for Sustainable Development (eBook, ePUB) Green Communication with Field-programmable Gate Array for Sustainable Development (eBook, ePUB)]() Bishwajeet PandeyGreen Communication with Field-programmable Gate Array for Sustainable Development (eBook, ePUB)54,95 €

Bishwajeet PandeyGreen Communication with Field-programmable Gate Array for Sustainable Development (eBook, ePUB)54,95 €![Advanced Field-Effect Transistors (eBook, ePUB) Advanced Field-Effect Transistors (eBook, ePUB)]() Advanced Field-Effect Transistors (eBook, ePUB)140,95 €

Advanced Field-Effect Transistors (eBook, ePUB)140,95 €![Spacer Engineered FinFET Architectures (eBook, ePUB) Spacer Engineered FinFET Architectures (eBook, ePUB)]() Sudeb DasguptaSpacer Engineered FinFET Architectures (eBook, ePUB)50,95 €

Sudeb DasguptaSpacer Engineered FinFET Architectures (eBook, ePUB)50,95 €![Sensors for Next-Generation Electronic Systems and Technologies (eBook, ePUB) Sensors for Next-Generation Electronic Systems and Technologies (eBook, ePUB)]() Sensors for Next-Generation Electronic Systems and Technologies (eBook, ePUB)51,95 €

Sensors for Next-Generation Electronic Systems and Technologies (eBook, ePUB)51,95 €![Nanoscale Semiconductors (eBook, ePUB) Nanoscale Semiconductors (eBook, ePUB)]() Nanoscale Semiconductors (eBook, ePUB)49,95 €

Nanoscale Semiconductors (eBook, ePUB)49,95 €-

-

-

The book provides the basic theory and operating principles of FinFET devices and technology. Accordingly, the book systematically presents an overview of FinFET device architecture and manufacturing processes, detailed formulation of FinFET electrostatic and dynamic device characteristics for IC design and manufacturing.

Hinweis: Dieser Artikel kann nur an eine deutsche Lieferadresse ausgeliefert werden.

Dieser Download kann aus rechtlichen Gründen nur mit Rechnungsadresse in A, B, BG, CY, CZ, D, DK, EW, E, FIN, F, GR, HR, H, IRL, I, LT, L, LR, M, NL, PL, P, R, S, SLO, SK ausgeliefert werden.

Hinweis: Dieser Artikel kann nur an eine deutsche Lieferadresse ausgeliefert werden.

Produktdetails

- Produktdetails

- Verlag: Taylor & Francis eBooks

- Seitenzahl: 338

- Erscheinungstermin: 15. Juli 2020

- Englisch

- ISBN-13: 9780429998089

- Artikelnr.: 59751266

- Verlag: Taylor & Francis eBooks

- Seitenzahl: 338

- Erscheinungstermin: 15. Juli 2020

- Englisch

- ISBN-13: 9780429998089

- Artikelnr.: 59751266

- Herstellerkennzeichnung Die Herstellerinformationen sind derzeit nicht verfügbar.

Samar K. Saha received a PhD in Physics from Gauhati University, India, and

MS in Engineering Management from Stanford University, CA. Currently, he is an

Adjunct Professor in the Electrical Engineering Department at Santa Clara University,

CA, and Chief Research Scientist at Prospicient Devices, CA. Since 1984, he has

worked in various technical and management positions for National Semiconductor,

LSI Logic, Texas Instruments, Philips Semiconductors, Silicon Storage Technology,

Synopsys, DSM Solutions, Silterra USA, and SuVolta. He has also worked as a

faculty member in the Electrical Engineering Departments at Southern Illinois

University at Carbondale, IL; Auburn University, AL; the University of Nevada at

Las Vegas, NV; and the University of Colorado at Colorado Springs, CO. He has

authored more than 100 research papers. He has also authored one book, Compact

Models for Integrated Circuit Design: Conventional Transistors and Beyond (CRC

Press, 2015); one book chapter on Technology Computer-Aided Design (TCAD),

"Introduction to Technology Computer-Aided Design," in Technology Computer

Aided Design: Simulation for VLSI MOSFET (C.K. Sarkar, ed., CRC Press, 2013);

and holds 12 US patents. His research interests include nanoscale device and process

architecture, TCAD, compact modeling, devices for renewable energy, and TCAD

and R&D management.

Dr. Saha served as the 2016-2017 President of the Institute of Electrical and

Electronics Engineers (IEEE) Electron Devices Society (EDS) and is currently serving

as the Senior Past President of EDS, J.J. Ebers Award Committee Chair, and

EDS Fellow Evaluation Committee Chair. He is a Fellow of IEEE and a Fellow

of the Institution of Engineering and Technology (IET, UK), and a Distinguished

Lecturer of IEEE EDS. Previously, he has served as the Junior Past President of EDS;

EDS Awards Chair; EDS Fellow Evaluation Committee Member; EDS President-

Elect; Vice President of EDS Publications; an elected member of the EDS Board of

Governors; Editor-In-Chief of IEEE QuestEDS; Chair of EDS George Smith and Paul

Rappaport Awards; Editor of Region 5&6 EDS Newsletter; Chair of EDS Compact

Modeling Technical Committee; Chair of EDS North America West Subcommittee

for Regions/Chapters; a member of the IEEE Conference Publications Committee;

a member of the IEEE TAB Periodicals Committee; and the Treasurer, Vice Chair,

and Chair of the Santa Clara Valley-San Francisco EDS chapter.

Dr. Saha served as the head guest editor for the IEEE Transactions on

Electron Devices (T-ED) Special Issues (SIs) on Advanced Compact Models and

45-nm Modeling Challenges and Compact Interconnect Models for Giga Scale

Integration; and as a guest editor for the T-ED SI on Advanced Modeling of Power

Devices and their Applications and the IEEE Journal of Electron Devices

Society (J-EDS) SI on Flexible Electronics from the Selected Extended Papers at

2018 IFETC. He has also served as a member of the editorial board of the World

Journal of Condensed Matter Physics (WJCMP), published by the Scientific

Research Publishing (SCIRP).

MS in Engineering Management from Stanford University, CA. Currently, he is an

Adjunct Professor in the Electrical Engineering Department at Santa Clara University,

CA, and Chief Research Scientist at Prospicient Devices, CA. Since 1984, he has

worked in various technical and management positions for National Semiconductor,

LSI Logic, Texas Instruments, Philips Semiconductors, Silicon Storage Technology,

Synopsys, DSM Solutions, Silterra USA, and SuVolta. He has also worked as a

faculty member in the Electrical Engineering Departments at Southern Illinois

University at Carbondale, IL; Auburn University, AL; the University of Nevada at

Las Vegas, NV; and the University of Colorado at Colorado Springs, CO. He has

authored more than 100 research papers. He has also authored one book, Compact

Models for Integrated Circuit Design: Conventional Transistors and Beyond (CRC

Press, 2015); one book chapter on Technology Computer-Aided Design (TCAD),

"Introduction to Technology Computer-Aided Design," in Technology Computer

Aided Design: Simulation for VLSI MOSFET (C.K. Sarkar, ed., CRC Press, 2013);

and holds 12 US patents. His research interests include nanoscale device and process

architecture, TCAD, compact modeling, devices for renewable energy, and TCAD

and R&D management.

Dr. Saha served as the 2016-2017 President of the Institute of Electrical and

Electronics Engineers (IEEE) Electron Devices Society (EDS) and is currently serving

as the Senior Past President of EDS, J.J. Ebers Award Committee Chair, and

EDS Fellow Evaluation Committee Chair. He is a Fellow of IEEE and a Fellow

of the Institution of Engineering and Technology (IET, UK), and a Distinguished

Lecturer of IEEE EDS. Previously, he has served as the Junior Past President of EDS;

EDS Awards Chair; EDS Fellow Evaluation Committee Member; EDS President-

Elect; Vice President of EDS Publications; an elected member of the EDS Board of

Governors; Editor-In-Chief of IEEE QuestEDS; Chair of EDS George Smith and Paul

Rappaport Awards; Editor of Region 5&6 EDS Newsletter; Chair of EDS Compact

Modeling Technical Committee; Chair of EDS North America West Subcommittee

for Regions/Chapters; a member of the IEEE Conference Publications Committee;

a member of the IEEE TAB Periodicals Committee; and the Treasurer, Vice Chair,

and Chair of the Santa Clara Valley-San Francisco EDS chapter.

Dr. Saha served as the head guest editor for the IEEE Transactions on

Electron Devices (T-ED) Special Issues (SIs) on Advanced Compact Models and

45-nm Modeling Challenges and Compact Interconnect Models for Giga Scale

Integration; and as a guest editor for the T-ED SI on Advanced Modeling of Power

Devices and their Applications and the IEEE Journal of Electron Devices

Society (J-EDS) SI on Flexible Electronics from the Selected Extended Papers at

2018 IFETC. He has also served as a member of the editorial board of the World

Journal of Condensed Matter Physics (WJCMP), published by the Scientific

Research Publishing (SCIRP).

Chapter 1

Introduction...........................................................................................1

Chapter 2 Fundamentals of Semiconductor

Physics............................................25

Chapter 3 Multiple-Gate Metal-Oxide-Semiconductor (MOS)

System..............85

Chapter 4 Overview of FinFET Device

Technology......................................... 133

Chapter 5 Large Geometry FinFET Device

Operation..................................... 151

Chapter 7 Leakage Currents in

FinFETs........................................................... 215

Chapter 8 Parasitic Elements in

FinFETs.......................................................... 231

Chapter 9 Challenges to FinFET Process and Device Technology

.................. 257

Chapter 10 FinFET Compact Models for Circuit

Simulation..............................277

Index

.......................................................................................................................309

Introduction...........................................................................................1

Chapter 2 Fundamentals of Semiconductor

Physics............................................25

Chapter 3 Multiple-Gate Metal-Oxide-Semiconductor (MOS)

System..............85

Chapter 4 Overview of FinFET Device

Technology......................................... 133

Chapter 5 Large Geometry FinFET Device

Operation..................................... 151

Chapter 7 Leakage Currents in

FinFETs........................................................... 215

Chapter 8 Parasitic Elements in

FinFETs.......................................................... 231

Chapter 9 Challenges to FinFET Process and Device Technology

.................. 257

Chapter 10 FinFET Compact Models for Circuit

Simulation..............................277

Index

.......................................................................................................................309

Chapter 1

Introduction...........................................................................................1

Chapter 2 Fundamentals of Semiconductor

Physics............................................25

Chapter 3 Multiple-Gate Metal-Oxide-Semiconductor (MOS)

System..............85

Chapter 4 Overview of FinFET Device

Technology......................................... 133

Chapter 5 Large Geometry FinFET Device

Operation..................................... 151

Chapter 7 Leakage Currents in

FinFETs........................................................... 215

Chapter 8 Parasitic Elements in

FinFETs.......................................................... 231

Chapter 9 Challenges to FinFET Process and Device Technology

.................. 257

Chapter 10 FinFET Compact Models for Circuit

Simulation..............................277

Index

.......................................................................................................................309

Introduction...........................................................................................1

Chapter 2 Fundamentals of Semiconductor

Physics............................................25

Chapter 3 Multiple-Gate Metal-Oxide-Semiconductor (MOS)

System..............85

Chapter 4 Overview of FinFET Device

Technology......................................... 133

Chapter 5 Large Geometry FinFET Device

Operation..................................... 151

Chapter 7 Leakage Currents in

FinFETs........................................................... 215

Chapter 8 Parasitic Elements in

FinFETs.......................................................... 231

Chapter 9 Challenges to FinFET Process and Device Technology

.................. 257

Chapter 10 FinFET Compact Models for Circuit

Simulation..............................277

Index

.......................................................................................................................309