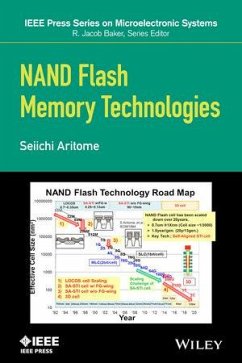

NAND Flash Memory Technologies (eBook, PDF)

Versandkostenfrei!

Sofort per Download lieferbar

122,99 €

inkl. MwSt.

Weitere Ausgaben:

PAYBACK Punkte

0 °P sammeln!

* Offers a comprehensive overview of NAND flash memories, with insights into NAND history, technology, challenges, evolutions, and perspectives * Describes new program disturb issues, data retention, power consumption, and possible solutions for the challenges of 3D NAND flash memory * Written by an authority in NAND flash memory technology, with over 25 years' experience

Dieser Download kann aus rechtlichen Gründen nur mit Rechnungsadresse in A, B, BG, CY, CZ, D, DK, EW, E, FIN, F, GR, HR, H, IRL, I, LT, L, LR, M, NL, PL, P, R, S, SLO, SK ausgeliefert werden.